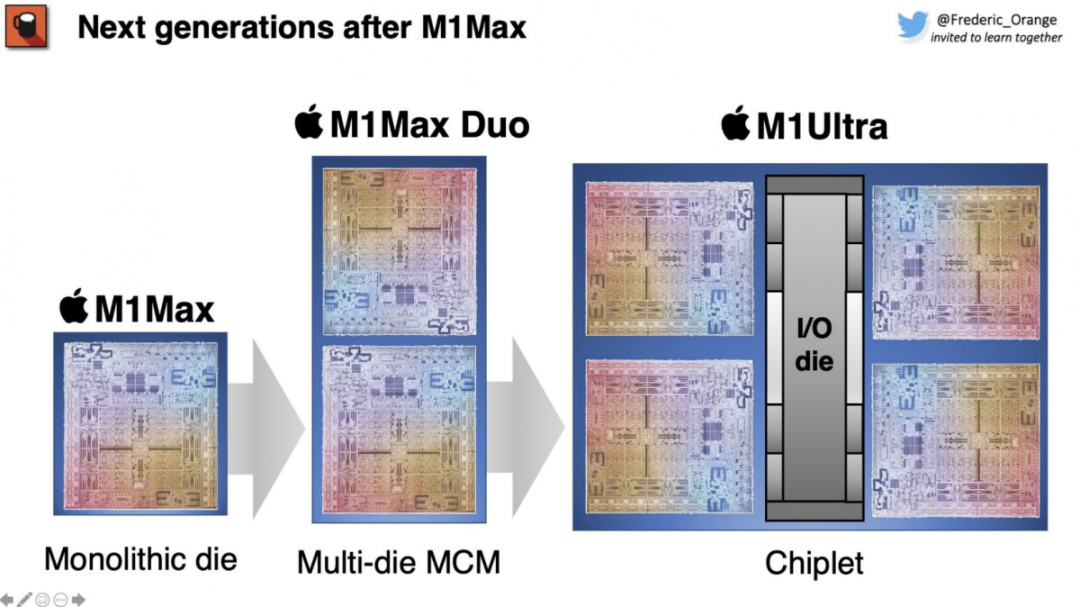

在当下的半导体行业中,Chiplet(芯粒)设计已经成为行业主流,推动Chiplet发展的AMD获益良多。苹果在春季发布会上推出自研的M1Ultra芯片,通过UltraFusion架构将两个M1Max芯片拼在一起,使芯片的各项硬件指标翻倍,性能也得到大幅提升。

▎据说,这就是M1Max+M1 Max ?

苹果该不会是把两个M1Max 给粘一起了吧?

还别说,苹果还真就是这么干的。而且M1Ultra的多核跑分也刚刚好是M1Max的两倍,苹果本来就牛的起飞的芯片,变得加倍起飞了。

在芯片设计风格上,“舍得堆料”是苹果一贯的特色。

从微架构级别的堆内存,到更宏观一些的堆CPU、GPU核心,再到直接将两个完整的SoC堆在一起,苹果的设计理念并不是在随机地发展着,其背后是一条连贯的逻辑线。

因此,当两个M1Max芯片堆砌而成的M1Ultra呈现在我们面前时,一切是如此意料之外而又情理之中。

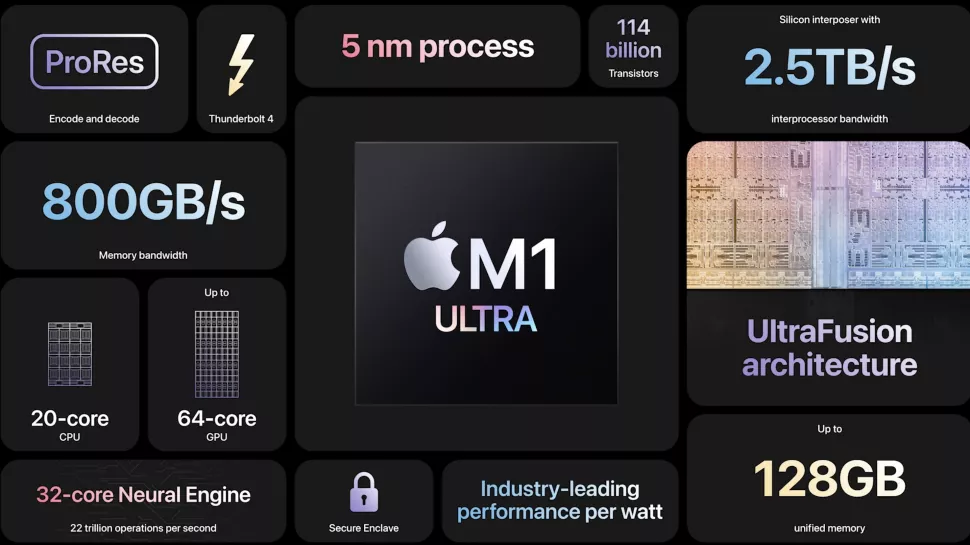

性能方面,苹果M1Ultra支持128GB高带宽、低延迟的统一内存,内建20个CPU核心、64个GPU核心和32核神经网络引擎,每秒可提供高达22万亿次运算,其GPU性能是苹果M1芯片的8倍,比最新的16核PC台式机高90%。

相比之下,英特尔的数据中心级超算GPUPonte Vecchio、英伟达刚刚发布还热乎着的H100GPU,晶体管数量也“仅有”区区1000亿和800亿。

苹果这次选择的是“1+1”的方式,一方面,苹果用产品表明了自己力挺基于芯粒的技术方向的态度;另一方面,又叫板了UCIe:“芯粒的互联,我已经搞定了”。

▎“胶水”粘期的芯片,能有多牛皮?

两颗芯片缝合的中间,有一层薄薄的“胶水”。苹果官方称之为UltraFusion 。而别看这玩意这么薄,它能够承载2.5TB/s的数据通信量。

注意,是2.5TB!每秒!

当然“胶水”不仅是简单的物理连接结构,封装架构中还有特别牛皮技术。

第一项就是在UltraFusion芯片中,加入新的低RC(电容x电阻=传输延迟)金属层,它能够在毫米互连尺度上提供更好的片间信号完整性。与传统的多芯片模块(MCM)等封装解决方案相比,UltraFusion的中介层在逻辑芯粒之间或逻辑芯粒和存储器堆栈之间提供密集且短的金属互连。拥有片间完整性更好、能耗更低,同时还能以更高的频率运行。

第二项就是互连功耗控制,UltraFusion使用可关闭的缓冲器(Buffuer),进行互连缓冲器的功耗控制,有效降低暂停的互连线的能耗。

第三项是优化高纵横比的硅通孔(TSV),TSV是硅中介层技术中另一个非常关键部分。UltraFusion/CoWoS-S5通过使用重新设计的TSV,优化传输特性,以适合高速SerDes传输。

▎压力给到了传统芯片制造商

苹果的UltraFusion技术充分结合封装互连技术、半导体制造和电路设计技术,为整合面积更大、性能更高的算力芯片提供巨大的想象空间。

同时,M1Ultra的成功,会让传统的芯片制造商,感受到更大的压力。

作为未来半导体的发展方向,先进封装技术在最近几年已得到广泛的应用,同时获得大众的认可。

特别是越来越多厂商加入到自研芯片的大军,如何提升Chiplet之间的互联、再到与HBM或DDR内存之间的带宽,也是延续摩尔定律的焦点。

文章为竞泰分析观点,不构成投资建议,请谨慎阅读