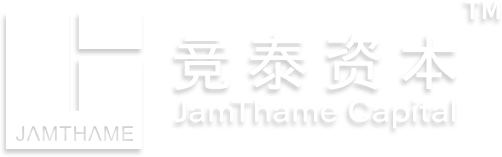

In the current semiconductor industry, Chiplet design has become the mainstream of the industry, and AMD, which promotes the development of Chiplet, has benefited a lot. Apple launched its self-developed M1Ultra chip at the spring conference. The two M1Max chips were put together through the UltraFusion architecture, which doubled the hardware indicators of the chip and greatly improved its performance.

▎It is said that this is M1Max+M1 Max?

Could it be that Apple glued the two M1Max together?

Not to mention, that's exactly what Apple does. And the multi-core running score of M1Ultra is just twice that of M1Max . Apple's original chip that has taken off has become doubled.

In terms of chip design style, "willing to stack" is a consistent feature of Apple.

From the micro-architecture-level heap memory to the more macro heap CPU and GPU cores, to the direct stacking of two complete SoCs, Apple's design philosophy is not developing randomly, but a coherent line behind it. logic line.

Therefore, when two M1Max chips stacked M1Ultra presented in front of us, everything is so unexpected and reasonable.

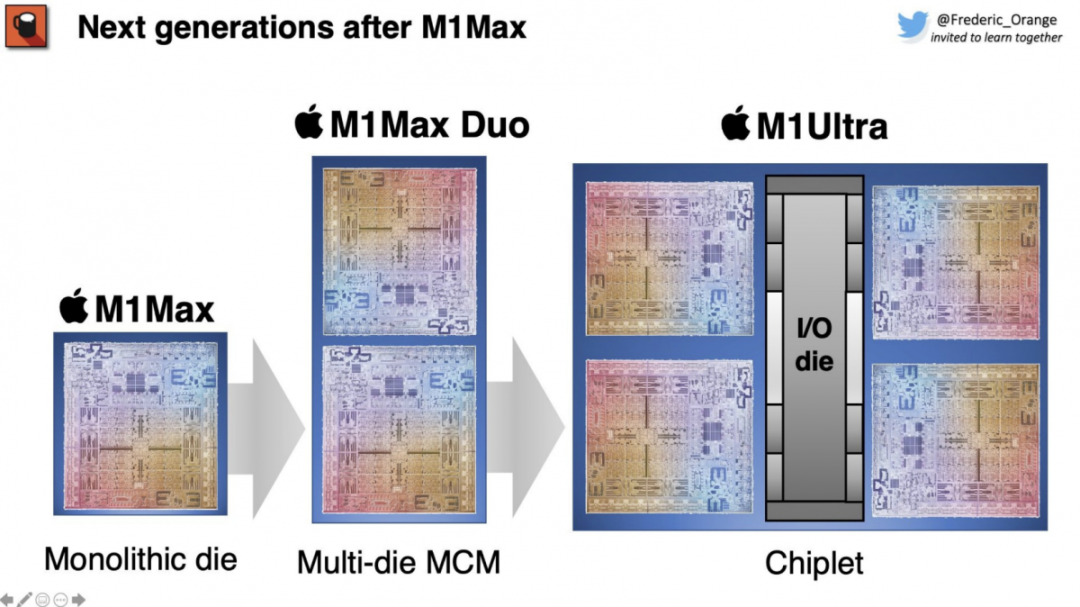

In terms of performance, the Apple M1Ultra supports 128GB of high-bandwidth, low-latency unified memory, built-in 20 CPU cores, 64 GPU cores and a 32-core neural network engine, which can provide up to 22 trillion operations per second. 8 times the M1 chip and 90% higher than the latest 16-core PC desktops.

In contrast, Intel's data center-level supercomputing GPU Ponte Vecchio and Nvidia have just released the hot H100GPU, and the number of transistors is "only" 100 billion and 80 billion.

Apple chose the "1+1" approach this time. On the one hand, Apple used products to show its support for the technology direction based on chips; on the other hand, it challenged UCIe : "The interconnection of chips, I It's done."

▎How much leather can a chip with "glue" sticky period be?

There is a thin layer of "glue" in the middle of the stitching between the two chips. Apple officially calls it UltraFusion. And despite how thin this thing is, it can carry 2.5TB/s of data traffic.

Note, it's 2.5TB! every second!

Of course, "glue" is not only a simple physical connection structure, but also special cowhide technology in the packaging structure.

The first is the addition of a new low RC (capacitance x resistance = propagation delay) metal layer in the UltraFusion chip, which provides better inter-chip signal integrity at the millimeter interconnect scale. Compared to traditional packaging solutions such as multi-chip modules (MCMs), UltraFusion's interposers provide dense and short metal interconnects between logic dies or between logic dies and memory stacks. Better inter-chip integrity, lower power consumption, and the ability to run at higher frequencies.

The second item is interconnect power consumption control. UltraFusion uses a buffer that can be closed to control the power consumption of interconnect buffers, effectively reducing the power consumption of suspended interconnect lines.

The third item is optimizing high-aspect ratio through-silicon vias (TSVs), another very critical part of silicon interposer technology. UltraFusion/CoWoS-S5 optimizes transmission characteristics for high-speed SerDes transmission by using a redesigned TSV.

▎ Pressure is placed on traditional chip manufacturers

Apple's UltraFusion technology fully combines packaging interconnect technology, semiconductor manufacturing and circuit design technology to provide a huge imagination space for integrating computing chips with larger areas and higher performance.

At the same time, the success of M1Ultra will make traditional chip manufacturers feel more pressure.

As the development direction of future semiconductors, advanced packaging technology has been widely used in recent years and has been recognized by the public.

In particular, more and more manufacturers have joined the army of self-developed chips. How to improve the interconnection between Chiplets and the bandwidth with HBM or DDR memory is also the focus of continuing Moore's Law.

The article is an analysis point of view of Jingtai and does not constitute investment advice. Please read it carefully.